# AN OPTIMIZED THREE-PHASE MULTILEVEL INVERTER TOPOLOGY WITH SEPARATE LEVEL AND PHASE SEQUENCE GENERATION **PART**

Ravula .Anitha M.Tech .Power Electronics Student Vinuthna Institute of Technology and Science Warangal, India,

V. Prashanth. Assistant Professor, Department of EEE Vinuthna Institute of Technology and Science Warangal, India,

#### **ABSTRACT**

This project presents an optimized, 3-φ, multilevel inverter (MLI) topology. The proposed system is derived by cascading the level part with the phase sequence generation part. Further, it can be operated at any required level depending upon the configuration of the level generation part. Thus, for higher level operation extra components are required at the level generation part only. Therefore, number of components required for the proposed MLI is lower than the conventional 3-φ MLI topologies for higher level operation. Further, the level generation part is shared by the three phases equally. This eliminates the possibility of phase unbalance. The working principle and the operation of the proposed MLI are supported with the simulation and experimental validations. Further, the proposed optimized MLI is also compared with the conventional 3-\phi MLIs to prove its advantage.

Keywords: Common mode voltage, multilevel inverter, new topology, 3-φ.

#### 1.1 INTRODUCTION

OVER a few decades, multilevel inverters (MLIs) are at the focal point of continuing research due to the features of improved power quality, reduced total harmonic distortion, high modularity, minimum filter requirement, reduced switching loss, low dv/dtstress, etc., . In literature, the authors have proposed multitude of the 1-φ and 3-φ, MLI configurations with respect to the component minimization and level maximization. The most common technique adopted in the 1-φ systems is the separation of polarity and level generation parts. However, this technique is yet to be applied in the 3-φ MLIs for the reduction and increment in the number of components and levels, respectively. It is well known that in case of conventional 3-φ, MLI solutions such as neutral point clamped (NPC) and flying capacitor (FC), the number of components is quite high. Further, it increases in the multiple of three with the increment in the number of levels. This makes the NPC and FC MLIs expensive for their higher level operation. Further, the capacitor voltage balancing becomes a challenging task for more than 3-level operation. Most of these issues are addressed by the cascaded MLIs (CMLIs) employing isolated dc sources asymmetrical with an configuration . Asymmetrical configuration helps to achieve more number of levels at the output with reduced number of components. However, the dc voltage sources in the CMLIs are not equally shared by the three phases. This may introduce an unbalance in the 3-φ output of the CMLI . Apart from this, the number of the isolated dc voltage sources required is also high for the CMLI configurations. To address the above-mentioned issues, a new optimized 3-optimized 3-MLI configuration is proposed in thispaper. The proposed 3-φ MLI is derived by using the concept of level and polarity generation, as used in the case of 1-φ MLIs. However, the task of polarity generation part is executed by the phase sequence generation part in the proposed 3-φ, MLI. Usage of separate level and phase sequence generation parts helps in reducing the number of components significantly in the proposed system. Also, for a higher level operation of the proposed MLI, the modification is required at the level generation

part only. Thus, the number of extra components required for the higher level operation is reduced and is less than the multiple of three. Further, the proposed MLI can also be operated in asymmetrical configuration. This will further help in maximizing the number of levels at the output. Moreover, the level generation part is common to the three phases. This eliminates the probability of an unbalance in the 3-φ output. Rest of the paper consists of four more sections.

# WORKING PRINCIPLE OF PROPOSED **TOPOLOGY**

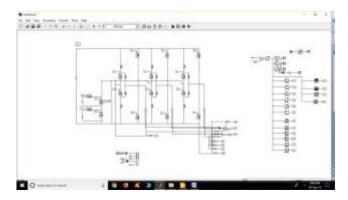

The circuit diagram of the proposed optimized MLI configuration for m-level operation. It consists of two parts, (i) level generation part (LGP) and (ii) phase sequence generation part (PSGP). The LGP is realized using two identical basic units (BUs) connected in series, as can be seen. BUs used in LGP consists of "n" number of series connected subunits or cells with a dc voltage source,

Fig. 1. (a) Circuit schematic for the proposed mlevel MLI. (b) Configuration of top/bottom BU.

Each subunit/cell again consists of dc voltage source and a pair of complementary switches. For, e.g., the ith subunit/cell contains a dc voltage source with the magnitude Vi and a pair of complementary power switches, Sxi and Sxi' [where, x = 1 for top BU and x = 2 for bottom BU and i  $(1, 2, \ldots, n)$ ]. Thus, for the realization of complete LGP, the total numbers of the switches and sources required are "4n" and "2(n + 1)," respectively. The advantages of having multiple

dc sources are improved reliability, power extraction capability, and capacitor voltage balancing capability. These isolated dc sources can be realized using multi-winding transformer followed by multiple diode bridge rectifiers or solar PV sources . Discontinuity in the input current of the PV source can be taken care of by connecting a buffer capacitor across the PV source and suitable PWM strategy. Further, it can be observed from Fig. 1 that the LGP has three output buses/terminals which are referred as bus 1, 2, and 3. The top BU of LGP is connected between buses 1 and 2, whereas the bottom BU is connected between buses 2 and 3. These three buses are also the common link between LGP and PSPG. The PSGP consists of a T-type inverter with three input and output terminals. The input terminals are directly connected to three buses 1, 2, and 3. And the output terminals are connected to 3- $\varphi$ , Y-connected load. Thus, any phase P can be connected to bus Q (where P (A, B, C) and Q (1, 2, 3)) using power switch SQP. Further, the switches connecting bus 1 and 3, i.e., S1P and S3P are realized with single MOSFETs. And the switch S2P is realized using the antiseries connection of two MOSFETs as indicated. Thus, PSGP is realized using 12 MOSFETs, which remains fixed for any level operation of the proposed MLI. Therefore, the total number of the switches "NSW" required for the realization of proposed MLI with "n" number of subunits in each BU is given by

$$N_{SW} = 4n + 12.$$

Similarly, the total number of dc voltage sources "NSRC" required by the proposed MLI is given by NSRC = 2(n + 1). Now with the increasing value of "n", the number of voltage levels at the output will increase and it also depends upon the magnitudes of the dc voltage sources. Depending upon the magnitudes of the dc voltage sources, the proposed MLI can have two types configurations, as described in the following sections.

# ASYMMETRICAL CONFIGURATION

In this configuration, the magnitude of the dc voltage source in ith subunit is given by

$$V_i = 2^{i-1}V_{dc}$$

.

Further, the maximum number of levels, "NLA" generated by the MLI in case of asymmetrical configuration is given as

$$N_{LA} = 2^n + 2.$$

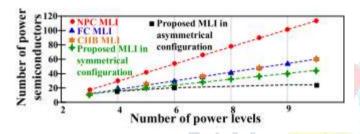

To justify the number of levels, the space vector (SV) diagram of the proposed inverter with n = 3both symmetrical and asymmetrical configurations. The thick red line the operating boundary of the proposed MLI. Even if the vectors outside the operating boundary are not proposed considered. the MLI still advantageous when compared to conventional MLI topologies such as NPC, FC, and CHB MLI. A graph is plotted between the number of levels and power semiconductor switches for both conventional

Fig. 3. Plot between the number of switches versus number of levels for the proposed topology and the conventional MLI topologies.

MLI MLI configurations and proposed (symmetrical and asymmetrical). It can be observed from that the proposed configuration can realize more number of levels with reduced number of switches in both symmetrical and asymmetrical configurations. The proposed MLI is also compared with the conventional NPC MLI for four-level operation,. It can be observed from that the proposed MLI requires reduced number of switches and driver circuits for its four-level operation. The total voltage rating of the devices is also less for the proposed MLI. Reduced number of conducting switches results in reduced conduction loss compared to NPC MLI. Similarly, reduced requirement of driver circuit reduces the driver circuit loss and cost for the proposed MLI as compared to the NPC MLI. Apart from this, the proposed MLI has higher efficiency than NPC for four-level operation, as can be seen . (The efficiency calculations are done considering both systems to be of 4.67 kW rating and driven at 25

kHz switching frequency with the loss calculation methods. The IGBT and diode models are also used from . Loss calculations were done for both NPC and the proposed MLI.

# SYMMETRICAL CONFIGURATION

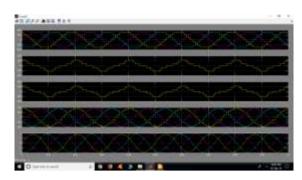

According to (4) and Fig. 2(a), the proposed MLI operates at 6-level in a symmetrical configuration for n = 3. This can be justified from the simulation results showing the line-to-line voltage waveform in Fig. 4(a) for symmetrical configuration of the proposed MLI. Further, the output voltages of top and bottom BUs, "Vot" and "Vob", respectively, are also shown in Fig. 4(b) and (c). It can be observed that four voltage levels are present in the waveforms of "Vot" and "Vob ." Therefore, the operation in symmetrical configuration using three subunits in each BU is also supported by the simulation results. Moreover, the simulated three phase-to-neutral voltages and load currents are also shown in Fig. 4(d) and (e), respectively.

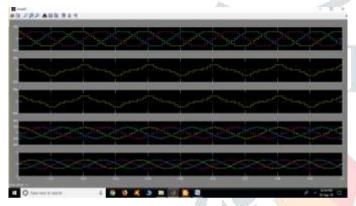

## ASYMMETRICAL CONFIGURATION

The proposed MLI is also simulated for asymmetrical configuration with n = 3. In this condition, the proposed MLI operates at 10-level, according to This is also supported by the simulated line-to-line voltage waveforms. Further, asymmetrical configuration the voltages of top and bottom BUs are presented .The presence of eight voltage levels in the waveforms of "Vot" and "Vob" supports the operation of the proposed MLI in asymmetrical configuration. Further, the simulation results showing phase-to-neutral voltages and load currents are presented.

#### RESULTS

Fig. 4. Simulation results showing (a) line-to-line voltages, (b) output voltage of top BU, (c) output voltage of bottom BU, (d) phase-to-neutral voltages and (e) load current waveforms of the proposed  $3-\varphi$ MLI in symmetrical operation.

Fig. 5. Simulation results showing (a) line-to-line &&voltages, (b) output voltage of top BU, (c) output voltage of bottom BU, (d) phase-to-neutral voltages and (e) load current waveforms of the proposed 3- $\varphi$  MLI in asymmetrical operation.

## **CONCLUSION**

This paper presents an optimized 3- $\varphi$  MLI configuration with reduced number of component. The prominent features of the proposed MLI are as follows.

- 1) The proposed MLI configuration is built by cascading LGP and PSGP.

- 2) For higher level operation, only switches required are at the BUs only, which resides in the LGP. This reduces the requirement of extra devices compared to conventional topologies.

- 3) Also, each dc voltage source in the presented MLI topology is equally shared by all the phases. Thus, any chance of inter-phase asymmetry is avoided. The above-mentioned points support that the proposed MLI is an optimized configuration for 3-φ operation with reduced number of switches. However, the proposed configuration is

operated by using the SVs up to the red line only. The further work with an improved PWM strategy, which takes all the SVs in account, will be presented in the regular paper. This will further increase the number of levels at the output and linearity can be maintained in the overmodulation region with improved dc-bus utilization.

### REFERENCES

- [1] J. Rodriguez, J. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," IEEE Trans. Ind. Elect., vol. 49, no. 4, pp. 724-738, Aug. 2002. 7418 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 32, NO. 10, OCTOBER 2017

- [2] K. K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu, and S. Jain, "Multilevel inverter topologies with reduced device count: A review," IEEE Trans. Power Elect., vol. 31, no. 1, pp. 135–151, Jan. 2016.

- [3] B. Wu and M. Narimani, High-Power Converters and AC Drives. Hoboken, NJ, USA: Wiley, 2016.

- [4] S. S. Fazel, S. Bernet, D. Krug, and K. Jalili, "Design and comparison of 4-kV neutral-pointclamped, flying-capacitor, and series-connected hbridge multilevel converters," IEEE Trans. Ind. Appl., vol. 43, no. 4, pp. 1032–1040, Jul./Aug. 2007.

- [5] L. Wang, D. Zhang, Y. Wang, B. Wu, and H. S. Athab, "Power and voltage balance control of a novel three-phase solid-state transformer using multilevel cascaded h-bridge inverters microgrid applications," IEEE Trans. Power Elect., vol. 31, no. 4, pp. 3289–3301, Apr. 2016.

- [6] Y. Shi, R. Li, Y. Xue, and H. Li, "Highfrequency-link-based grid-tied PV system with small DC-link capacitor and low-frequency ripple-free maximum power point tracking," IEEE Trans. Power Elect., vol. 31, no. 1, pp. 328–339, Jan. 2016.

- [7] S. Essakiappan, H. S. Krishnamoorthy, P. Enjeti, R. S. Balog, and S. Ahmed, "Multilevel medium-frequency link inverter for utility scale photovoltaic integration," IEEE Trans. Power Elect., vol. 30, no. 7, pp. 3674–3684, Jul. 2015.

- [8] M. D. Manjrekar, P. K. Steimer, and T. A. Lipo, "Hybrid multilevel power conversion system: A competitive solution for high-power applications," IEEE Trans. Ind. Appl., vol. 36, no. 3, pp. 834–841, May/Jun. 2000.

- [9] S. K. Chattopadhyay and C. Chakraborty, three-phase asymmetric "Performance of cascaded bridge (16:4:1) multilevel inverter," IEEE Trans. Ind. Elect., vol. 62, no. 10, pp. 5983– 5992, Oct. 2015.

- [10] K.-m Tsang and W.-i Chan, "Single DC source three-phase multilevel inverter using reduced number of switches," IET Power Elect., vol. 7, no. 4, pp. 775–783, Apr. 2014.

- [11] M. F. Kangarlu and E. Babaei, "A generalized cascaded multilevel inverter using series connection of submultilevel inverters," IEEE Trans. Power Elect., vol. 28, no. 2, pp. 625-636, Feb. 2013.

- [12] P. Sharma, P. K. Peter, and V. Agarwal, "Exact maximum power point tracking of partially shaded PV strings based on current equalization concept," in Proc. 38th IEEE Photovoltaic Spec. Conf., Austin, TX, USA, 2012, pp. 001411-001416.

- [13] V. Sonti, S. Jain, and S. Bhattacharya, "Analysis of modulation strategy for the minimization of leakage current in the PV grid connected cascaded multi-level inverter," IEEE Trans. Power Elect., vol. 32, no. 2, pp. 1156-1169, Feb. 2017.

- [14] S. Clemente, "A simple tool for the selection of IGBTs for motor drives and UPSs," in Proc. 10th Annu. Appl. Power Electron. Conf. Expo., Dallas, TX, USA, 1995, vol. 2, pp. 755-764.

Ravula anitha born was Ellandhakunta, karimnagar, Telangana, India In 1993 .She is currently working towards the postgraduate degree in power electronics at vinuthna Institute

of Technology and Sciences, Kakatiya University. She is currently a Researcher in the field of Electronics and and Power quality.

V.Prashanth born 30.06.1988 received Btech and mtech degrees in electrical 2011 engineering in and 2014 respectively. from intuh currently working asst.prof in VITS Hasanparthy.